¶ CPU IP

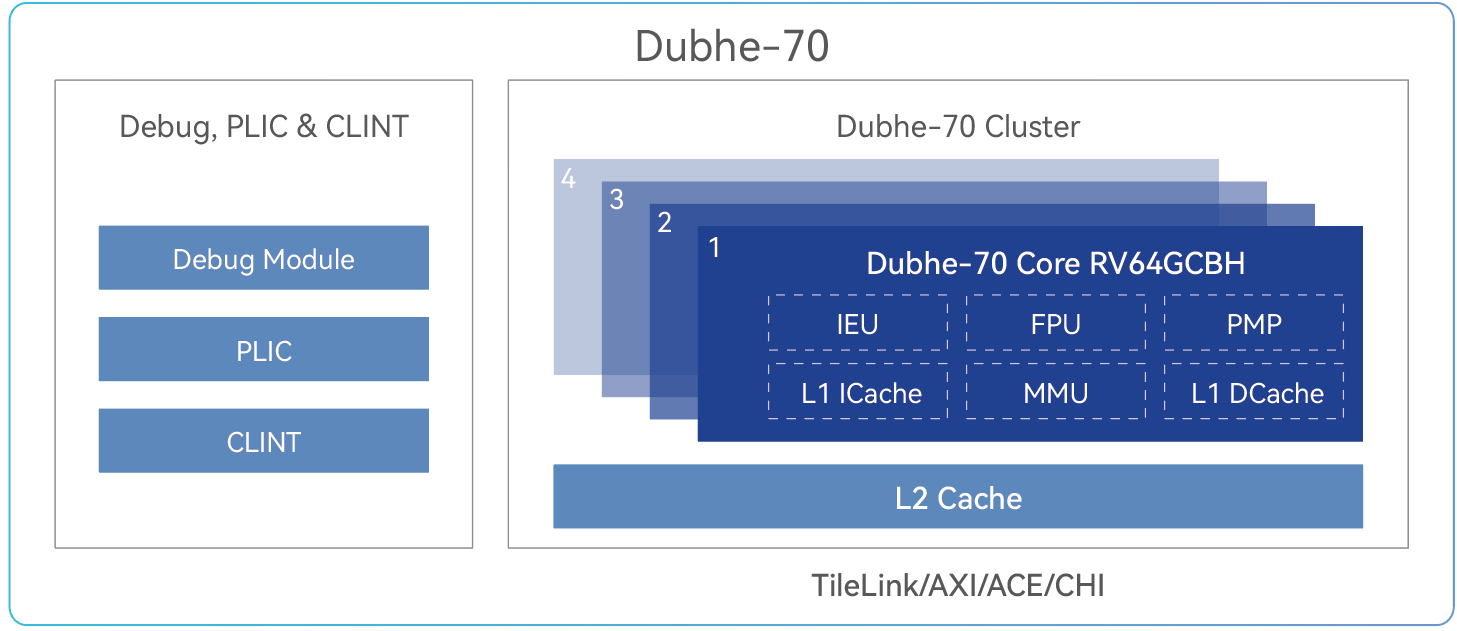

¶ Dubhe-70

¶ Overview

StarFive Dubhe-70 is a 9+ stage, 3-issue, out-of-order CPU IP that supports the rich RISC-V instruction set, RV64GCBH_Zicond_Zicbom_Zicboz_Zicbop.

With a score of 7.2 SPECInt2006/GHz, Dubhe-70 targets applications that require highly energy-efficient computation, including mobile, desktop, AI, and automotive.

Dubhe-70 has been pre-integrated and verified, making it easy to use for SoC development work.

With options of single-core, dual-core, or quad-core in a single cluster with memory coherency, Dubhe-70 is highly scalable.

¶ Block Diagram

¶ Learn More

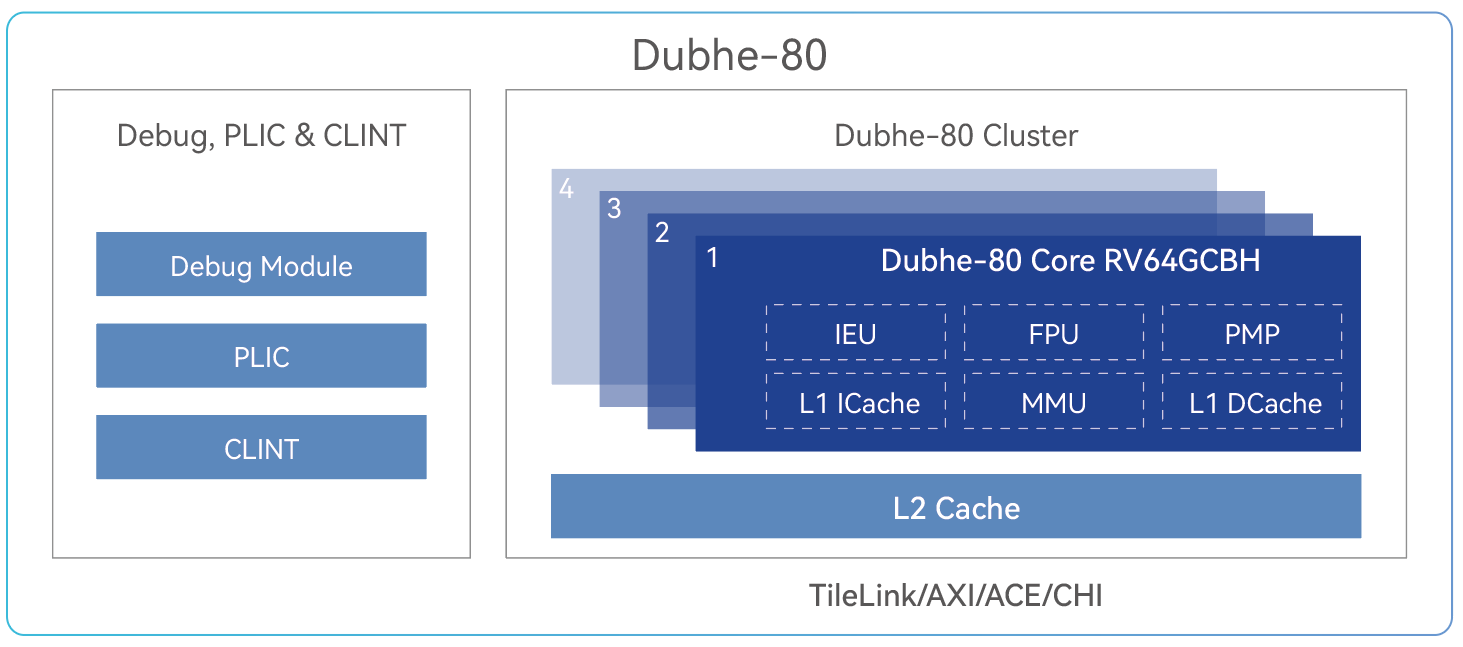

¶ Dubhe-80

¶ Overview

StarFive Dubhe-80 processor features a 9+ stage, 3-issue, out-of-order pipeline, fully compliant with a rich set of RISC-V extensions of RV64GCBH_Zicond_Zicbom_Zicboz_Zicbop. With a score of 8.5 SPECInt2006/GHz, Dubhe-80 is designed for mobile, desktop, AI, and automotive applications that require highly energy-efficient computation.

Dubhe-80 has been pre-integrated and verified, making it easy to use for SoC development work. With options of single-core, dual-core, or quad-core in a single cluster with memory coherency, Dubhe-80 is highly scalable.

¶ Block Diagram

¶ Learn More

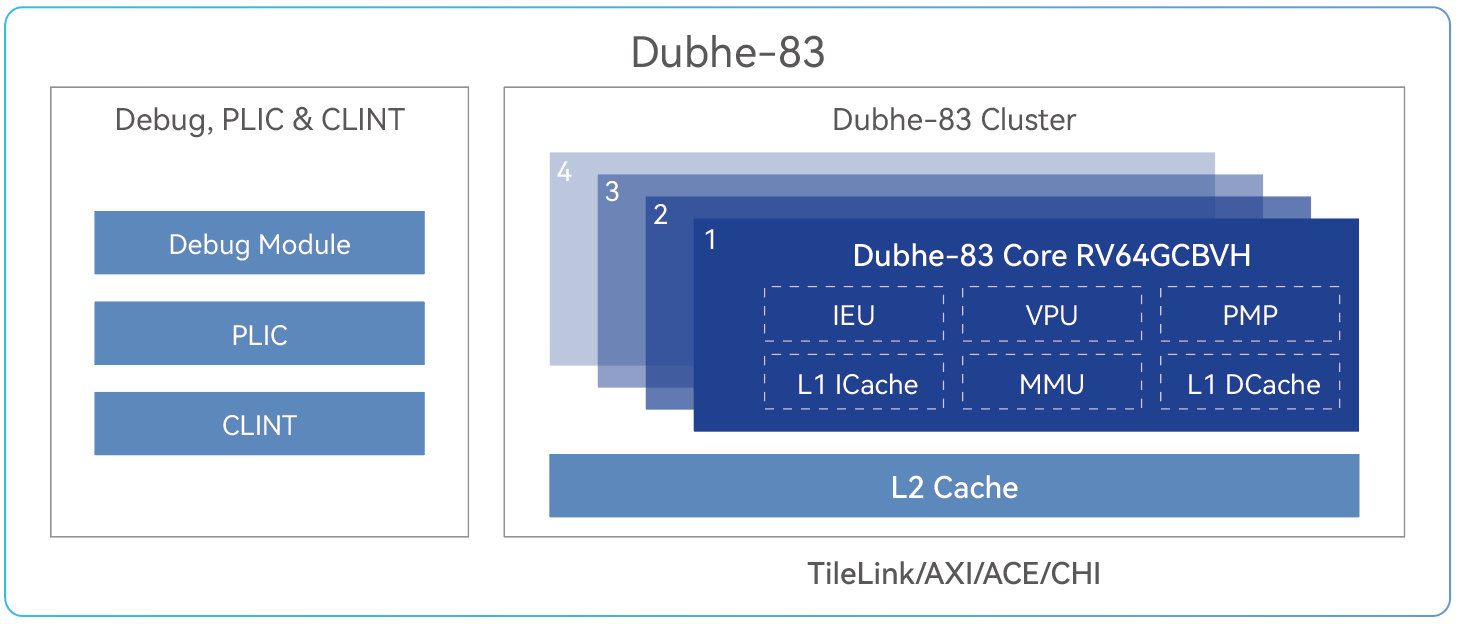

¶ Dubhe-83

¶ Overview

StarFive Dubhe-83 CPU IP features a 10+ stage pipeline, 3-issue, and out-of-order pipeline, follows the RVA23 Profile, and supports all extensions of Vector Crypto. With a score of 8.5 SPECInt2006/GHz, Dubhe-83 targets applications that require highly energy-efficient computation, including mobile, desktop, AI, and automotive.

Dubhe-83 has been pre-integrated and verified, making it easy to use for SoC development work. With options of single-core, dual-core, or quad-core in a single cluster with memory coherency, Dubhe-83 is highly scalable.

¶ Block Diagram

¶ Learn More

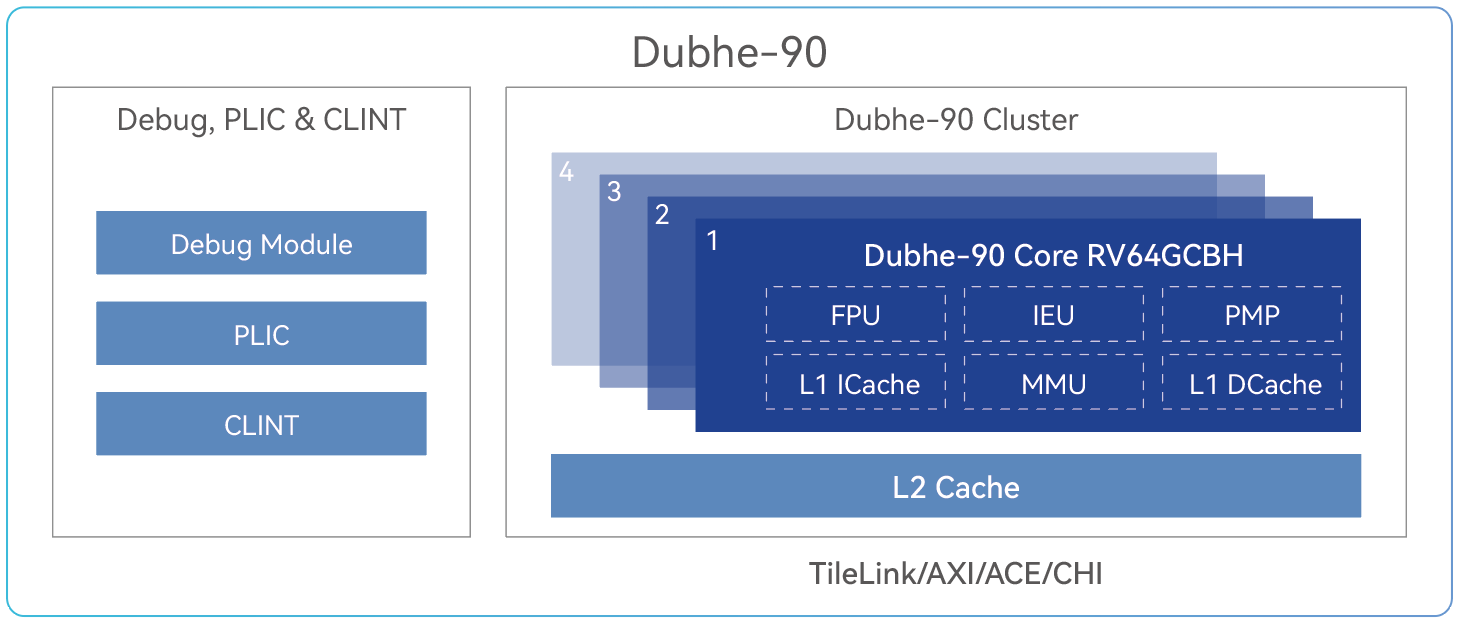

¶ Dubhe-90

¶ Overview

StarFive Dubhe-90 processor features an 11+ stage and 5-issue pipeline, superscalar, and deep out-of-order execution, and supports standard RISC-V RV64GCBH extensions. With a score of 9.4 SPECInt2006/GHz, Dubhe-90 is designed for high-performance computing scenarios and devices, such as data centers, PCs, mobile devices, high-performance network communications, and machine learning.

Dubhe-90 has been pre-integrated and verified, making it easy to use for SoC development work. With options of single-core, dual-core, or quad-core in a single cluster with memory coherency, Dubhe-90 is highly scalable.

¶ Block Diagram

¶ Learn More

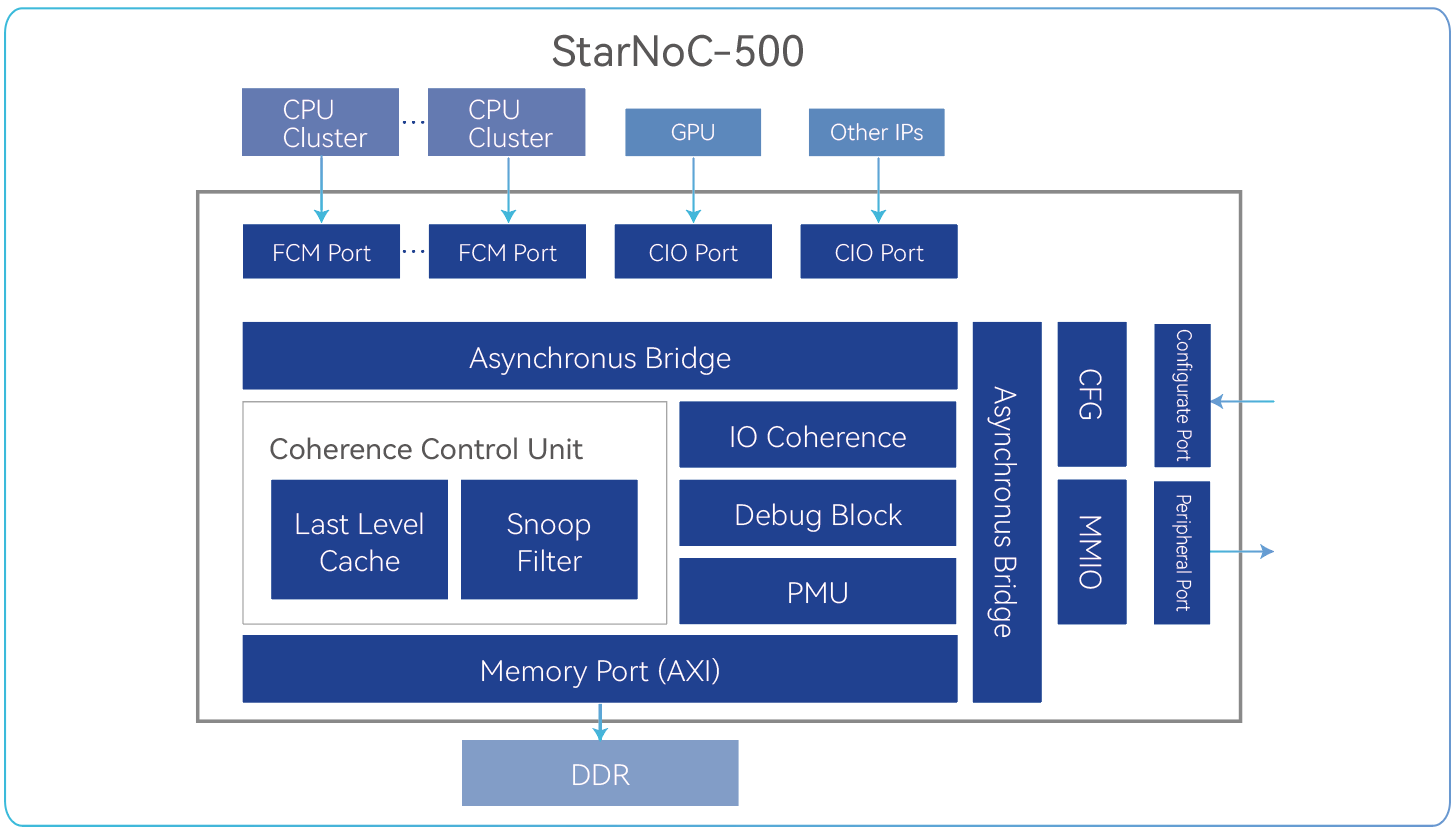

¶ Interconnect Fabric IP

¶ StarNoC-500

¶ Overview

StarNoC-500 is StarFive's first self-developed interconnect fabric IP with cache coherence support, supporting the construction of multi-cores and SoC to provide cache coherence NoC, connecting multiple CPU clusters, IO devices, and DDR, and maintaining cache coherence within the SoC.

- Providing NoC with cache coherence: connecting multiple CPU clusters, IO devices, and DDR, and maintaining cache coherence within the SoC.

- High Performance: Provides Last Level Cache (LLC), offers Snoop Filter, improves the efficiency of coherence maintenance modules, and memory hierarchy performance.

- Efficient Data Exchange: Supports CPU and IO device sharing of LLC, simplifying CPU and IO data exchange and improving performance.

- Low Power Consumption: Supports LLC way shutdown, cache retention, and other low-power technologies.

- High Reliability: Snoop Filter and LLC support SEC-DED (Single Error Correction Double Error Detection).

- Control Interface Support (CFG & MMIO): CPU configuration of IO devices and on-chip SRAM reading; IO device access and configuration of on-chip interconnect coherence.

¶ Block Diagram

¶ Learn More

¶ StarNoC-700

¶ Overview

StarNoC-700 is StarFive's self-developed high-scalable, high-performance interconnect fabric IP supporting cache coherence, enabling the construction of a manycore SoC solution.

- Providing NoC with cache coherence: connecting up to 256 CPU cores, IO devices, and DDR, while maintaining cache coherence within the SoC scope

- High performance: providing a maximum of 512 MB Last Level Cache (LLC) with Snoop Filter, enhancing the efficiency of coherence maintenance modules and memory hierarchy performance.

- High scalability: employing mesh NoC to enhance expandability, and a dedicated control NoC to support control command transmission

- Low latency: adopting a semi-custom design approach to reduce NoC transmission latency.

- Efficient data exchange: supporting CPU and IO devices to share the LLC, simplifying CPU and IO data exchange, and improving performance

- Low power consumption: supporting low power consumption technologies such as LLC way shutdown and Architecture Clock Gating

- High reliability: Snoop Filter and LLC support ECC (SEC-DED, Single Error Correction Double Error Detection)

¶ Block Diagram

¶ Learn More

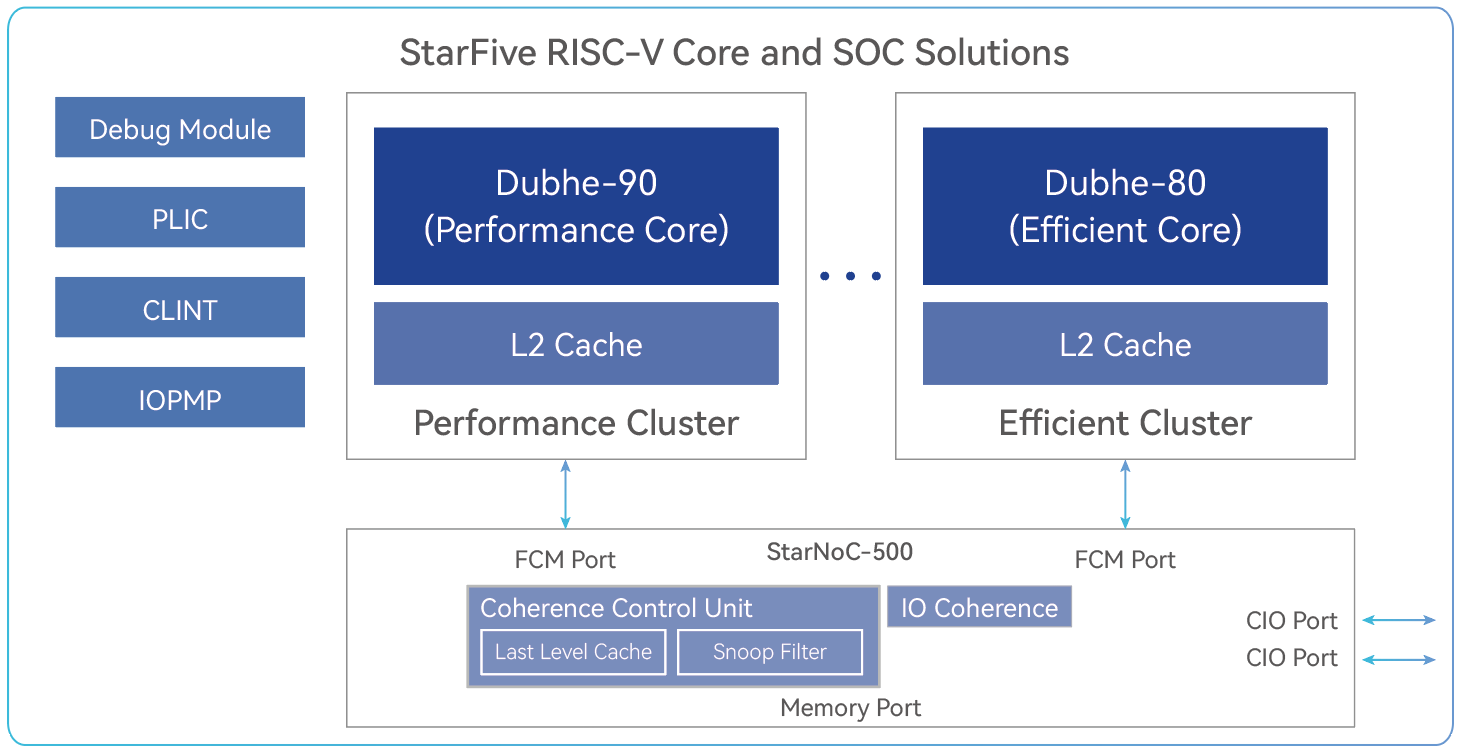

¶ Multi-Core Solution

¶ Overview

StarFive RISC-V Multi-Core Solution is a high-performance, high-bandwidth, low-latency SoC solution based on StarFive RISC-V CPU IP and Interconnect Fabric IP. This solution provides:

- RISC-V high performance core--Dubhe-90

- RISC-V high efficiency core--Dubhe-80

- High-speed Interconnect Fabric IP supporting cache coherency--StarLink-500

- RISC-V debug module

- RISC-V PLIC and CLINT

- Power management, security, virtualization (CPU), IO coherency, and memory subsystem.

¶ Block Diagram

¶ Learn More

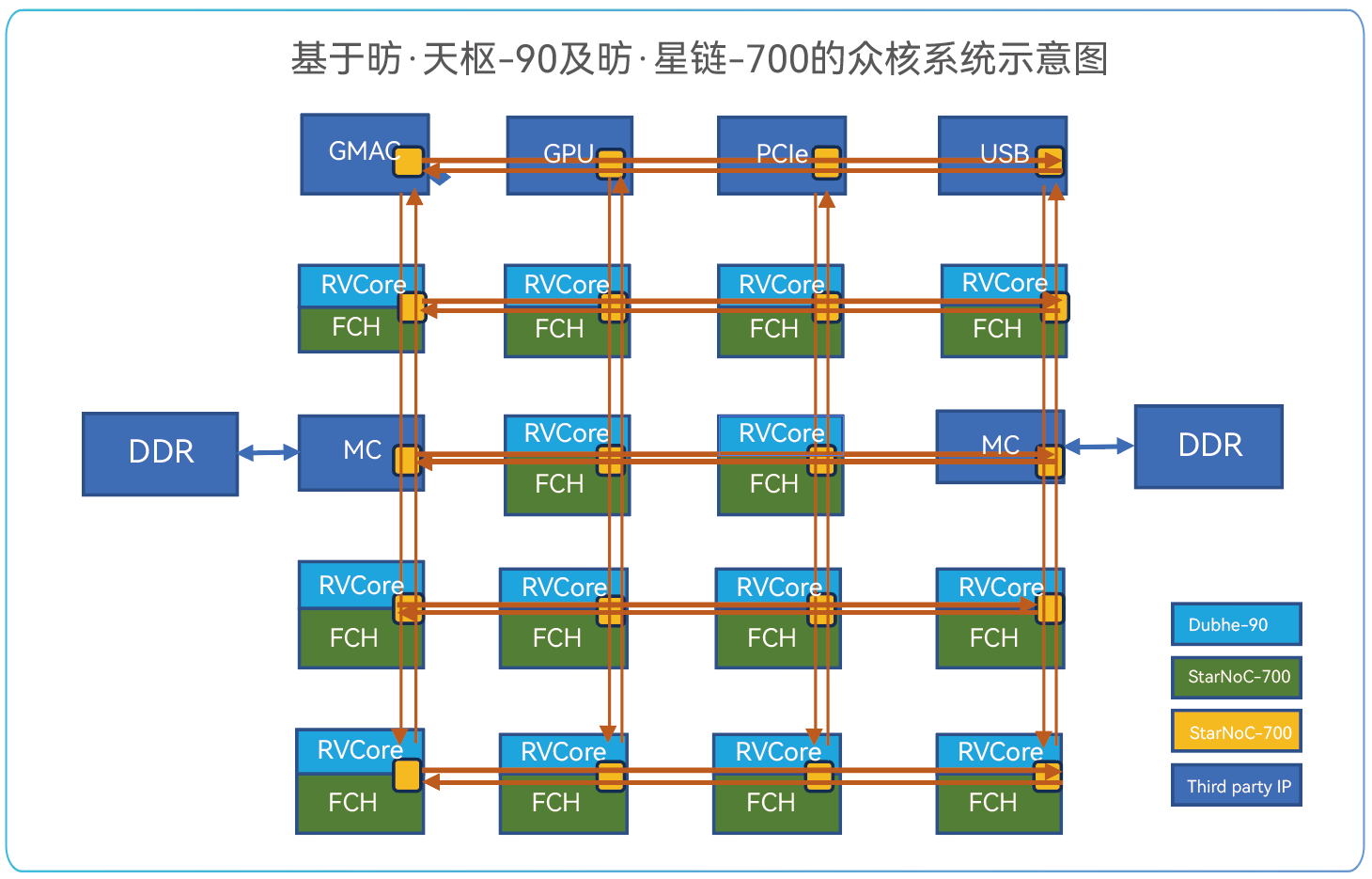

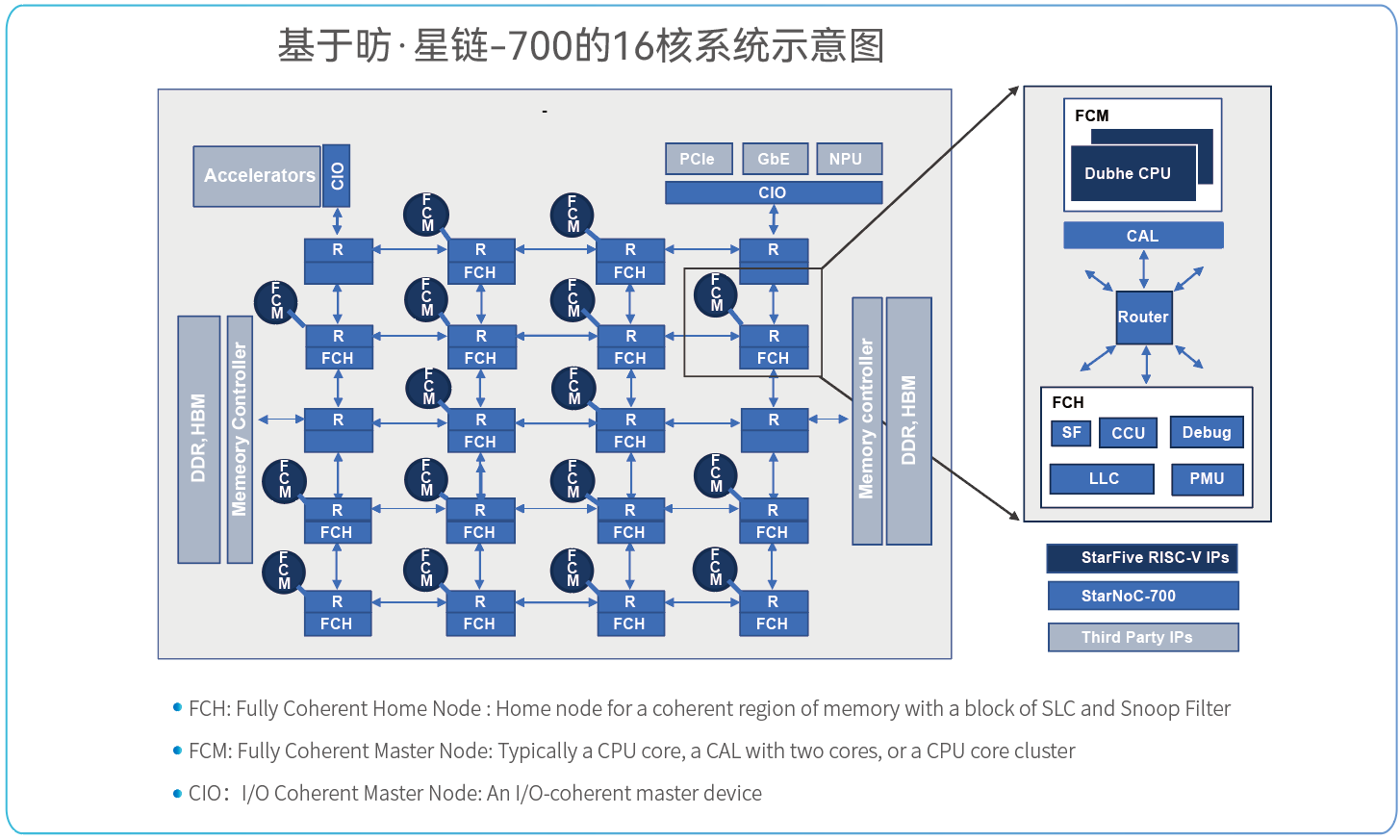

¶ Manycore Solution

A high-performance, high-bandwidth, low-latency RISC-V manycore SoC solution based on StarFive RISC-V CPU IPs and Interconnect Fabric IP. This solution provides:

- RISC-V high performance core--Dubhe-90

- High-speed interconnect fabric IP supporting cache coherence--StarLink-700

- RISC-V debug module interface

- RISC-V PLIC and CLINT

- Power management, security, virtualization, IO coherency, and memory subsystem.