# JH7110 SOC PLATFORM

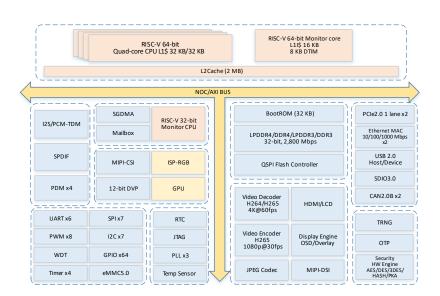

JH7110 is a RISC-V SoC platform. The SoC applies the mature 28 nm process technology and supports Linux operating system. It is featured for high performance, low power consumption and rich image and video processing capabilities.

# HIGH PERFORMANCE

The SoC carries 64-bit high performance quad-core RISC-V CPU (Single core performance equals to Arm Cortex-A55) The quad cores shares a 2 MB L2 cache, with work frequency up to 1.5 GHz.

# LOW POWER CONSUMPTION

The SoC is divided into 8 independent power domains. The CPU work frequency is software configurable based on scenario and requirement. The static power consumption of the SoC is 130 mW.

# RICH INTERFACES

The SoC is equipped with the following peripheral interfaces PCle 2.0, eMMC 5.0, HDMI 2.0, MIPI, USB 2.0/3.0, 10M/100M/1000M GMAC, SDIO 3.0 and so on.

# IMAGE/VIDEO PROCESSING

Integrated with StarFive independent ISP, the SoC is compatible with mainstream camera sensors. It provides the embedded image/video subsystem to support H.264/H.265/JPEG encoding. Its IMGBXE-4-32 GPU supports OpenCL, OpenGL ES, and Vulkan. JH7110 can complete a variety of complex image/video processing and intelligent visual calculations. It meets multiple visual real-time processing needs at the edge.

#### Consumer

- Personal SBC

- Noteboo

- Soft Routing

- NAS

- 00

#### Smart Home

- Smart Appliance

- Home Security

Remote Control

- Video SurveillanceSweeping Robot

# Industry

- Industrial Demo

- Industrial Demo

- Industrial Detection

- industrial Detection

- Smart Gateway

- Robot

- Smart Building

- Gaming

- Unmanned Shops

# **FEATURE**

# CPU SUBSYSTEM

- 64-bit high-performance RISC-V CPU quad-core

- -Support RV64GC RISC-V ISA

- -L1-cache: I\$32 KB/D\$32 KB

- -Cache coherence for quad-core

- RV64IMAC Monitor CPU monitor core

- -16 KB L1 I-Cache with ECC

- -8 KB DTIM with ECC

- -8 region physical memory protection

- 32-bit RISC-V CPU core

- -Support RV32IMFC RISC-V ISA

- -16 KB I-cache only

- L2-cache up to 2 MB cache size

- Dual DMA controllers support up to 16+4 channels

- Support Linux operating system

#### MEMORY AND STORAGE

- BUS RAM up to 256 KB

- DDR controller support 1 channel of x32

- -DDR4/3 and LPDDR4/3 for 2800 Mbps

- -Support 2 pieces of x16 or 1pcs of x32 devices

- -Support DDR memory density up to 8 GB

- QSPI controller support external flash memory

- -Support XIP mode and Page mode

- -Separate 1/2/4 data width

- -Support SPI Nor Flash size up to 16 MB

- -Support SPI Nand Flash size up to 2 GB

# GPU SUBSYSTEM

- Support OpenCL 3.0

- Support OpenGL ES 3.2

- Support Vulkan 1.2

#### SECURITY SUBSYSTEM

- Encrypt Engines: AES; DES/3DES; HASH; PKA

- Compliant with TRNG

- Support 256-bit random number generation

- 512 × 32-bit (2 KB) of OTP for key data on-die

#### CONNECTIVITY SUBSYSTEM

- 2x PCle2.0 controller with integrated PHY

- -X1 PCI Express Core

- -Support link rate of 5 GT/s per lane

- USB 2.0 host/device mode with high speed and full speed

- 2 × Ethernet GMAC for 10/100/1000 Mbps with RGMII

- 2 × SDIO 3.0/eMMC 5.0 host controllers

# VIDEO PROCESSING

# SUBSYSTEM

- Camera MIPI Interface

- -MIPI CSI-2 RX DPHY

- Up to 6 lanes of 1.5 Gbps

- Support 4D1C × 1 MIPI sensors Support 2D1C × 1 MIPI sensors

- Video Encoder

- -H.265 Encoder, 1080p@30fps

- -Support I/P type slice

- -High-performance CABAC encoding

- -Support ROI

- Video Decoder

- -Support 1-lane 4K@60fps or 8-lane 1080p@30fps decoding

- -Compatible with ITU-T H.264

- -Compatible with ISO/IEC 23008-2 H.265

- -Support 420 format, 8-bit/10-bit

- -Support I/P type slice

- -H.265 Main/Main10, L5.1

- -H.264 High/High10, L5.2

- ISP (Image Signal Process)

- -1 × MIPI CSI channel and 1 × DVP input

- -Up to 1080p@30fps CMOS RGB image sensor

- -ISP core support

- Defective pixel correction

- R/G/B LUT AE/AWB/AF

- Histogram analysis

- Lens Shading/Color Shading

- Sensor spatial crosstalk cancellation

- Global tone mapping/Spatial noise reduction

- Seamless digital scale down from 1/4x to 1x

- JPEG

- -Up to 290 MPixel/Sec for YUV420, 210

- MPixel/Sec for YUV422, 140 MPixel/Sec for YUV444

- -Bit rate 480 Mbps (MJPG 8M@30fps 422 1:8)

- -Compliant with Baseline/Extended sequential

- ISO/IEC 10918-1 JPEG

- -Compliant with Motion JPEG

- -Support from 16x16 pixels to 32 K × 32 K  $(32,768 \times 32,768)$

- 2 × CAN2.0B data rates up to 5 Mbps

#### AUDIO DSP

- Used for traditional audio/voice data algorithm processing

- 32-bit Audio DSP, support floating-point instructions

- 96 Kbytes DTCM, 96 Kbytes ITCM

- 16 Kbytes I-cache, 32 Kbytes D-cache

- Support internal DMA

- Support On-Chip Debug (OCD)

- 32 interrupts count

#### **PACKAGE**

• Body Size  $17 \times 17$  mm, 0.65 mm ball pitch, FCBGA 625 balls

# POWER SUPPLY

- 0.9 V core voltage

- 3.3 V/2.5 V/1.8 V I/O voltage

#### **CLOCK SOURCE**

- OSC 24 MHz for USB, GMAC and system main clock source

- OSC 32.768 KHz for RTC clock source

#### DISPLAY SUBSYSTEM

- Display

- $-1 \times HDMI 2.0$  up to 4 K@30fps display

- -RGB656, RGB888 I/F, up to

1080p@30fps

- -6 image layers shared by 2 display panels

- -1/64-64 times scaler (1/64 not covered)

- -MIPI TX DPHY lane with panel module

- MIPI Display Interface

- -MIPI TX DSI Controller for single output

- -MIPI TX DPHY support up to 4D1C lanes

- -Data rate support up to 2.5 Gbps

#### **AUDIO INTERFACE**

- 8 channel TX and RX I2S/PCM TDM

- Provide 4 sets of I2S/PCM I/F and support DMA interface

- Provide 2 sets of SPDIF and support RX mode and TX mode

- 4-channel PDM input for digital MIC application

- DAC output with PWM interface

#### PERIPHERAL

- 6 x UART

- 7 x I2C

- 7 x SPI

- 2 x SDIO

- 1 x DPI (Parallel RGB Display)

- 1 x PCM/I2S

- 7 x 32-bit WDT reset output

- 1 x temperature sensor

- 2 x INTC

- 8 x PWM outputs

- 1 x 32-bit WDT reset output

- 64 x GPIO

- 1 x DVP sensor input interface

- 3 x GPCLK outputs

#### **BOOT MODE**

- Boot Rom

- QSPI NOR/NAND Flash

- SD card/eMMC

- UART/USB/SD card for update

#### **DEVKITS**

JH-7110 also provides the Devkits along with the design schematics, PCB design reference and source files, as references to complete your own design. End solution providers are encouraged design their solutions based on the open resources we provided. On the other side, JH-7110 Devkits can also be used as the test platform to measure the JH-7110 overall specifications, including feature and performance to guarantee the accuracy and comprehensiveness of the test data.

JH-7110 Devkits provides the following components.

- Devkit mainboard

- Power adapter (12V/3A)

- LCD screen

- WiFi/Bluetooth pigtail

- Design schematics and source files

- RGB to VGA/LVDS/RGB (optional)

- Power rechargeable module (optional)

As the development kit associated with the JH-7110 SoC, Devkit is not available for sale individually. If you are interested, please contact your StarFive sales consultant for details.

# ABOUT RISC-V

The RISC-V Instruction Set Architecture (ISA) was born at the University of California, Berkeley in 2010 and was open-sourced in 2013. It is the fifth generation product of the Reduced Instruction Set Computing (RISC) series and has the advantages of being concise, open, modular, and scalable. Currently, the RISC-V International Association has 3,950 members from 70 countries, including chip designers, chip design service providers, system integrators, software service providers, research institutions, and investment institutions. RISC-V has been widely used in IoT devices and is beginning to gain market shares in high-end applications such as servers, communications, AI, autonomous driving, VR, and office equipment. According to the latest forecast by Semico Research, the cumulative shipments of RISC-V CPU cores worldwide will reach approximately 80 billion by 2025.

# ABOUT STARFIVE

Founded in 2018, StarFive is a Chinese local high-tech company with independent intellectual properties. As the leader of the RISC-V software and hardware ecosystem in China, StarFive provides world-leading products and solutions on RISC-V covering CPU IP, SoC, development boards, etc.

Since its establishment, StarFive has delivered a series of RISC-V products:

- Dubhe: Dubhe-90, the max performance commercial RISC-V CPU IP, and Dubhe-80, the high-efficiency RISCV CPU IP

- StarLink: StarLink-500, StarFive's first self-developed interconnect fabric IP

- **JingHong**: JH-7110/JH7110, the world's first high-performance multimedia processor for mass production

- VisionFive: VisionFive 2, the world's first SBC with an integrated 3D GPU for mass production

StarFive's products can be applied in a great variety of devices, scenarios, and industries including VDI, tablets, desktop/notebook computers, gateway, edge computing, industrial display, smart home, smart retail, smart energy, etc.

StarFive, rooting in China, and taking a broad view of the world, aims to become the leader and promoter of global RISC-V technology and ecosystem. StarFive will cooperate comprehensively with the global ecosystem partners in kernel layer, system service layer, frame layer, application layer and all other respects. StarFive will promote RISC-V technology into more high-end application areas and create more value for global developers and customers by leading the RISC-V development, and driving industry innovation.

技术文档: https://doc.rvspace.org/ Tech Doc: https://doc-en.rvspace.org/

Community: https://rvspace.org/ Official Web: https://www.starfivetech.com/ Sales: sales@starfivetech.com

021-50478300

Other: marketing@starfivetech.com